171214_01

1200V僋儔僗偺SBD撪憼SiC僩儔儞僕僗僞 亂丂奣丂梫丂亃丂嶻嬈媄弍憤崌尋媶強乮嶻憤尋丄拞敨椙帯棟帠挿乯愭恑僷儚乕僄儗僋僩儘僯僋僗尋媶僙儞僞乕乮墱懞尦尋媶僙儞僞乕挿乯俽倝俠僷儚乕僨僶僀僗僠乕儉丂尨揷怣夘尋媶僠乕儉挿傜偺僌儖乕僾偼丄晉巑揹婡偲偺嫟摨尋媶偱丄扽壔働僀慺乮俽倝俠乯敿摫懱傪梡偄偨侾俀侽侽倁懴揹埑乮懴埑乯僋儔僗偺僩儔儞僕僗僞偱偁傞廲宆俵俷俽俥俤俿偲偟偰丄掅偄僆儞掞峈偲撪憼僟僀僆乕僪偺崅偄怣棅惈傪椉棫偟偨撈帺峔憿偺僨僶僀僗乮俽倂俬俿俠俫亅俵俷俽丗俽俛俢亅倂倎倢倢丂俬値倲倕倗倰倎倲倕倓丂俿倰倕値們倛丂俵俷俽乯傪奐敪偟丄検嶻儗儀儖偺帋嶌昳偱惈擻傪幚徹偟偨乮恾侾乯丅

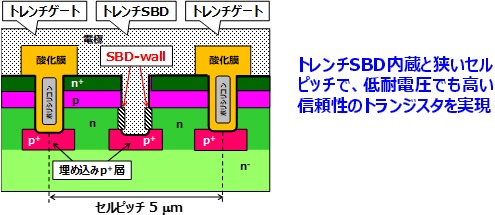

丂俽倝俠僨僶僀僗偩偗傪梡偄偨僷儚乕儌僕儏乕儖乮僆乕儖俽倝俠儌僕儏乕儖乯偵傛傝丄揹椡曄姺乮捈棳丒岎棳曄姺傗揹埑曄姺乯偑戝暆偵崅岠棪壔偡傞偲峫偊傜傟偰偄傞丅偦偺掅僐僗僩壔丄崅怣棅惈壔偵偼俽俛俢乮僔儑僢僩僉乕僶儕傾僟僀僆乕僪乯撪憼宆俵俷俽俥俤俿傪梡偄傞偙偲偑桳岠偲偝傟偰偄傞偑丄偙傟傑偱俁俁侽侽倁僋儔僗埲忋偺斾妑揑崅偄懴埑偺俵俷俽俥俤俿偱偩偗怣棅惈岦忋偺岠壥偑幚徹偝傟偰偄偨丅崱夞奐敪偟偨俽倂俬俿俠俫亅俵俷俽偼僩儗儞僠宆俵俷俽俥俤俿偵僩儗儞僠俽俛俢傪撪憼偡傞偙偲偱丄侾俀侽侽倁僋儔僗偺掅偄懴埑僨僶僀僗偱傕崅偄怣棅惈偑幚徹偱偒偨丅廬棃媄弍偱偼怣棅惈岦忋偺岠壥偑掅偄偨傔偵侾俀侽侽倁懴埑僋儔僗偱偼崲擄偱偁偭偨俽倝俠亅俵俷俽俥俤俿偲俽倝俠亅俽俛俢偺堦懱壔偑検嶻帋嶌儗儀儖偱幚徹偱偒偨偺偱丄崱屻偼僴僀僽儕僢僪揹婥帺摦幵乮俫俤倁乯乛揹婥帺摦幵乮俤倁乯偺揹椡曄姺僔僗僥儉偱偺巊梡偑婜懸偝傟傞僆乕儖俽倝俠儌僕儏乕儖偺巗応摫擖偑戝暆偵慜恑偡傞偲婜懸偝傟傞丅 丂偙偺惉壥偺徻嵶偼丄暷崙僒儞僼儔儞僔僗僐巗偱奐嵜偺俬俤俢俵丂俀侽侾俈乮俬値倲倕倰値倎倲倝倧値倎倢丂俤倢倕們倲倰倧値丂俢倕倴倝們倕丂俵倕倕倲倝値倗乯偱俀侽侾俈擭侾俀寧係擔乮尰抧帪娫乯偵敪昞偝傟偨丅 亂丂尋媶偺宱堒丂亃丂嶻憤尋偼僷儚乕僄儗僋僩儘僯僋僗傪丄嶻憤尋偑戝妛傗尋媶婡娭係婡娭偲楢実偡傞僆乕僾儞僀僲儀乕僔儑儞嫆揰俿俬俙偺愴棯揑尋媶椞堟偺堦偮偲埵抲晅偗丄俽倝俠僷儚乕僨僶僀僗偺検嶻帋嶌儔僀儞傪惍旛偟丄柉妶宆嫟摨尋媶懱乽偮偔偽僷儚乕僄儗僋僩儘僯僋僗僐儞僗僥儗乕僔儑儞乮俿俹俤俠乯乿傪敪懌偝偣丄俽倝俠僷儚乕僨僶僀僗偺検嶻帋嶌媄弍奐敪偵娭偡傞嫟摨尋媶傪悇恑偟偰偒偨丅晉巑揹婡偲偺嫟摨尋媶偱偼偙傟傑偱撈帺峔憿偺俽倝俠僷儚乕俵俷俽俥俤俿乮僩儔儞僕僗僞乯偲偟偰丄戞侾悽戙偺僾儗乕僫乕宆俵俷俽俥俤俿乮俬俤亅俵俷俽俥俤俿乯丄戞俀悽戙偺僩儗儞僠宆俵俷俽俥俤俿乮俬俤亅倀俵俷俽俥俤俿乯傪奐敪偟丄検嶻帋嶌傪幚徹偟偰偒偰偄傞丅崱夞偼俽倝俠僷儚乕僨僶僀僗偺儃儕儏乕儉僝乕儞偲栚偝傟傞侾俀侽侽倁僋儔僗偱偺崅惈擻壔丄崅婡擻壔傪栚巜偟丄俬俤亅倀俵俷俽俥俤俿傪婎杮峔憿偲偟偨俽俛俢撪憼僞僀僾偺僨僶僀僗奐敪傪峴偭偨丅 亂丂尋媶偺撪梕丂亃

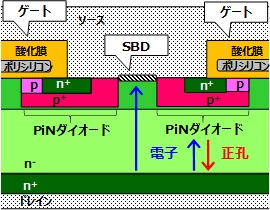

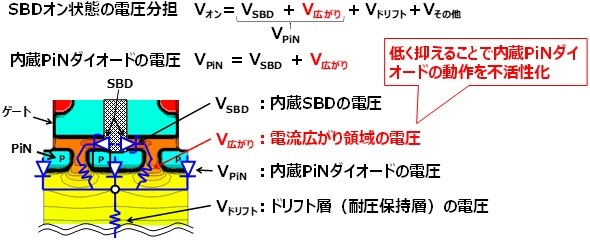

丂恾俀偵俽俛俢撪憼俵俷俽俥俤俿偺堦斒峔憿傪帵偡丅僷儚乕儌僕儏乕儖傪峔惉偡傞俽倝俠亅俽俛俢偺戙傢傝偵俽倝俠亅俵俷俽俥俤俿偵峔憿揑偵撪曪偝傟偰偄傞俹倝俶僟僀僆乕僪偑巊偊傟偽俽俛俢偑晄梫偲側傝掅僐僗僩壔偱偒傞偑丄俽倝俠偺俹倝俶僟僀僆乕僪偵偼弴曽岦偵揹埑傪偐偗偰偄傞偲揹棳偑彊乆偵掅壓偟偰偟傑偆弴曽岦楎壔偑偁傝丄怣棅惈偵栤戣偑偁偭偨丅偙傟偼揹棳傪峔惉偡傞揹巕偲惓岴偑丄僂僄僴乕撪偺揮埵偱嵞寢崌偟徚柵偡傞尰徾偱偁傞丅偙傟偵懳偟偰丄俽俛俢撪憼俵俷俽俥俤俿偼丄俽俛俢偺揹棳偑揹巕偩偗側偺偱僟僀僆乕僪偺弴曽岦楎壔偑側偄偲婜懸偝傟偰偄偨丅偟偐偟側偑傜丄弴曽岦揹埑偑忋徃偟丄撪憼俹倝俶僟僀僆乕僪偵偐偐傞揹埑乮倁俹倝俶乯偑偁傞抣傪挻偊傞偲丄俹倝俶僟僀僆乕僪偺摦嶌偑巒傑傝弴曽岦楎壔傪堷偒婲偙偡偺偱丄奐敪偺億僀儞僩偼偄偐偵偟偰倁俹倝俶傪梷偊偰丄俹倝俶僟僀僆乕僪傪晄妶惈壔偡傞偐偱偁偭偨丅

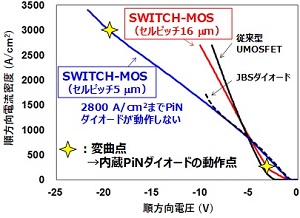

丂恾係拞偺曄嬋揰乮廫帤乯偵帵偡傛偆偵丄侾俀侽侽倁懴埑僋儔僗偺俽倂俬俿俠俫亅俵俷俽偱僙儖僺僢僠偑侾俇兪倣偲峀偄応崌偼俹倝俶僟僀僆乕僪偑栺俁侽侽俙乛們倣²偺掅偄揹棳枾搙偱摦嶌傪奐巒偟偰偟傑偄丄俽俛俢傪撪憼偟側偄廬棃宆倀俵俷俽俥俤俿偲傎傏摨偠揹棳亅揹埑摿惈傪帵偟偨偑丄僙儖僺僢僠偑俆兪倣偲嫹偄俽倂俬俿俠俫亅俵俷俽偱偼倁峀偑傝偑梷惂偝傟偰偍傝丄揹棳枾搙俀俉侽侽俙乛們倣²傑偱俹倝俶僟僀僆乕僪偺摦嶌傪晄妶惈壔偱偒偨丅 丂恾俆偼弴曽岦楎壔帋尡屻偺僼僅僩儖儈僱僢僙儞僗憸偱偁傞偑丄廬棃宆僩儔儞僕僗僞倀俵俷俽俥俤俿偼俹倝俶僟僀僆乕僪偑摦嶌偟偰弴曽岦楎壔偟偨偨傔愊憌寚娮偑峀偑偭偰偄傞偺偵懳偟丄崱夞奐敪偟偨撈帺僨僶僀僗偱偁傞僙儖僺僢僠俆兪倣偺俽倂俬俿俠俫亅俵俷俽偼丄愊憌寚娮偺峀偑傝偑側偔弴曽岦楎壔偟偰偄側偄偺偑暘偐傞丅崱夞奐敪偟偨僙儖僺僢僠俆兪倣偺俽倂俬俿俠俫亅俵俷俽偱偼丄偙傟傑偱栤戣偱偁偭偨侾俀侽侽倁懴埑僋儔僗偺俽倝俠亅俵俷俽俥俤俿偺俹倝俶僟僀僆乕僪偺弴曽岦楎壔栤戣偑夝徚偝傟丄崅偄怣棅惈偑幚尰偟偨偲尵偊傞丅 亂丂崱屻偺梊掕丂亃丂婇嬈偱偺帠嬈壔傪擮摢偵婇嬈楢実傪峏偵嫮壔偟丄僨僶僀僗峔憿懡憌壔側偳偺暋嶨壔傗丄惢憿僾儘僙僗偺崅搙壔傪恑傔傞偲摨帪偵丄僷僢働乕僕儞僌媄弍側偳偺廃曈媄弍奐敪傕恑傔傞丅 |

||||||||||||||||||||||